## Physics 214 INTRODUCTION TO LABORATORY ELECTRONICS Lecture 17

**Topics:** Digital-to-Analog and Analog-to-Digital Converters

Text: Bugg"\*3uv'gf kkqp+, 21.8"\*y kn'dg'j cpf gf "qw'kp"encuu+

In order to communicate between analog devices, such as measurement transducers, and digital devices, such as computers, it is necessary to convert between the two forms of information. The digital-to-analog converter (DAC) is a form of binary decoder whilst the analog-to-digital converter is a type of binary encoder.

| signal type                | interface                       | digital signal processor |

|----------------------------|---------------------------------|--------------------------|

|                            | $\leftarrow$ DAC $\leftarrow$   | digital output register  |

| $v_{in}(t)$ or $i_{in}(t)$ | $\rightarrow$ ADC $\rightarrow$ | digital input register   |

| Digital                    | $\rightarrow$                   | digital input register   |

| Digital                    | $\leftarrow$                    | digital output register  |

## **DIGITAL-to-ANALOG CONVERTERS**

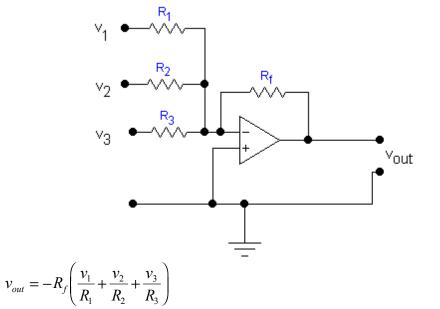

Today and tomorrow's labs will focus on DACs. In fact, we've already seen a basic circuit for a DAC when we studied the op-amp analog voltage summer in Lecture 12.

For a DAC, the three lines represent 3-bits if we let  $v_1$ ,  $v_2$ ,  $v_3$  be '0' or '1'. We just have to choose  $R_1$ ,  $R_2$ , and  $R_3$  so that the output voltage is proportional to the binary coded input.

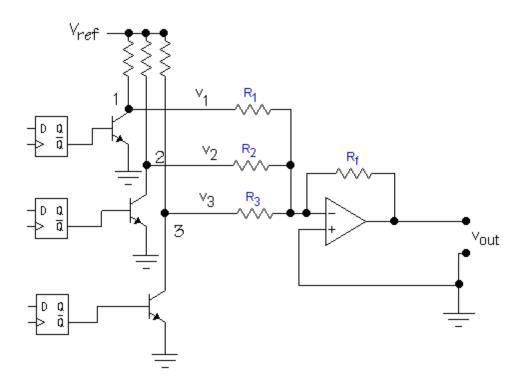

When the Q output of a flip-flop is LO (Q is HI), the switch is open and the voltage at the output of the switch is set to  $V_{ref}$  and when the  $\overline{Q}$  output is HI (Q is LO), the switch is closed and the output voltage of the switch is set to ground. So when switch 1 is open, switch 2 is closed and switch 3 is closed the binary word  $Q_3Q_2Q_1$  is 001. Now, we want  $v_{out}$  to be twice as large for 010 (which is  $2_{10}$ ) as it is for 001 and we want  $v_{out}$  to be four times as large for 100 (which is  $4_{10}$ ) as it is for 001. This will convert from the digital word to a meaningful analog output proportional to the binary number held in the digital register.

This is accomplished by setting  $R_1=R$ ,  $R_2=R/2$ ,  $R_3=R/4$ .

$$v_{out} = -V_{ref} \frac{R_f}{R} (Q_1 + 2Q_2 + 4Q_3)$$

$$Q_i = \begin{cases} 1 \text{ if } Q_i & \text{Hi} \\ 0 \text{ if } Q_i & \text{Lo} \end{cases} i = 1, 2, 3$$

The output of a 3-bit DAC is one of seven discrete voltages. For example, if  $V_{ref}=10V$ ,  $R=100k\Omega$  and  $R_f=1.00k\Omega$ :  $V_{ref}R_f/R = 10Vx1/100=100mV$

| $Q_3 \ Q_2 \ Q_1$ | V <sub>out</sub> |

|-------------------|------------------|

| 0 0 0             | 0                |

Note that only discrete values of output voltage can be produced by a DAC. In this example, -150mV can't be output, instead, -100mV and -200mV

| 0 0 1 | -100mV |

|-------|--------|

| 0 1 0 | -200mV |

| 0 1 1 | -300mV |

| 1 0 0 | -400mV |

| 1 0 1 | -500mV |

| 1 1 0 | -600mV |

| 1 1 1 | -700mV |

To describe a DAC, you need to specify the range of the output and the resolution. For example, a 12-bit DAC has input between 0 and 4095 ( $2^{12}$ -1=4095). So it has a resolution of 1/4095=0.02%. The range can be 0-5V for example, or -25V to +25V. If the range is 0-5V, then the smallest voltage step, also referred to as the resolution, is (5-0)/4095=0.00122V. If the range is -25 to 25, the resolution is (25 – (-25))/4095=0.012210V.

In order to use the DAC, one uses a conversion from a binary number to a voltage. For example, for the 12-bit DAC with the -25V to 25V range, if I need an output of 3V, what is the DAC input?

$V_{out} = DAC_{in} \times 0.012210V - 25V$

$DAC_{in} = (3V + 25V) / 0.012210 = 2293.2$

You can only have integer counts, so the closest count is 2293, which will give you: 2293x0.012210-25=2.99753V rather than 3.0000V.

How close to the desired voltage you get with a given DAC input depends on more than just the number of bits. The 'accuracy' depends how well the resistors match the values they should be. Mismatches among other things, lead to offset errors (quoted in number of least significant bits at 0 input, should be  $\frac{1}{2}$  LSB); linearity scale offsets (should be 1 LSB scale error, eg for 12-bits, scale error should be less than 1/4095); non-linearity ( $\pm \frac{1}{2}$  LSB means 1 LSB possible error); and non-monotonicity (want this less than  $\frac{1}{2}$ LSB).

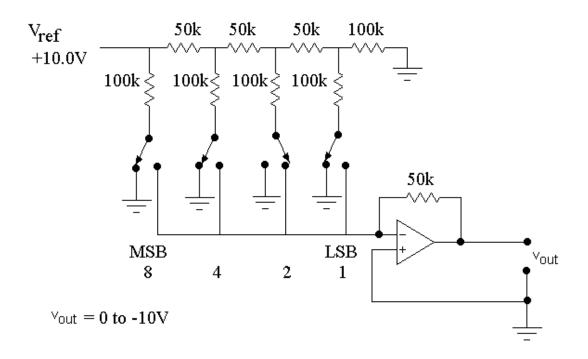

The difficulty with finding matching resistors means that in practice, many DACs use a R-2R ladder design which fulfills the same purpose but requires only 2 matched resistor values. In the example below, R=50 and 2R=100k.

An application with a DAC:

Waveform generator of any arbitrary shape with the shape stored in memory. The input to the DAC register is loaded from the memory at a given location (i.e. address); an address counter is incremented (by a counter) and then the DAC register loaded with the contents of the next memory location which is the next point on the waveform. The operation cycles through the entire set of memory locations holding the waveform shape, then repeats.

A common household device that uses a DAC to generate waveforms is a CD player.

## **Analog-to-Digital Converters**

The flip side of the DAC is the ADC. We'll start to explore this today and complete the discussion next time.

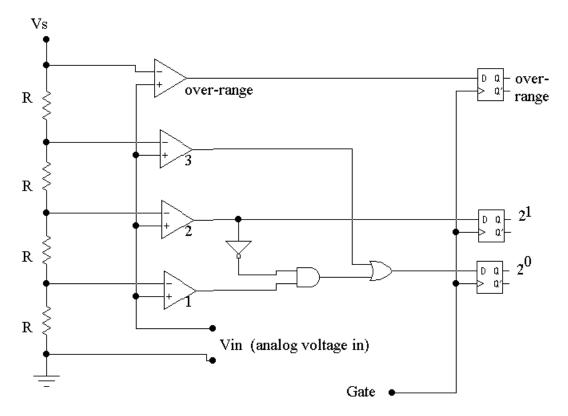

There are a variety of ADCs, but conceptually the most straightforward is the *flash ADC*. As the name implies it is the fastest type of ADC and also the most expensive type. The idea is simple: a pair of comparat ors can be used to set a digital bit if an analog signal lies between the two thresholds of the comparators. A flash ADC uses a whole string of comparators to digitize the analog signal.

This is a 2-bit Flash ADC. The comparato rs are set up such that the output of the comparat or is 1 if  $V_{in} > V_i$  and 0 if  $V_{in} < V_i$  where i=1,2,3 and  $V_i$  is the reference voltage for comparator i . The voltage steps are  $\Delta V = V_s/2^n = V_s/4$  for n=2. So here,  $V_1 = V_s/4$ ;  $V_2 = V_s/2$ ;  $V_3 = 3/4 V_s$ . Hence,  $\Delta V = V_{MAX}/(2^n-1) = 1/3 V_{MAX}$  and  $V_{MAX} = 3/4 V_s$ . In practice, one uses many more bits than 2.

As with DACs, one specifies the resolution in terms of bits or a percentage=100%/(2<sup>n</sup>-1); the input voltage range is specified and knowing those two pieces of information, the voltage resolution is  $\Delta V = (V_{MAX} - V_{MIN})/(2^n-1)$ , be found.

For example, an 8-bit FADC with a -5 to +5V has a voltage resolution of 10V/255=0.0392V. If a signal has a height of 3.000V, the ADC=(3.000-(-5.0)V)/0.0392=204.08. It is truncated to 204. If you read 105 on the ADC, to what voltage does it correspond? V=105 x 0.0392+(-5V)=-0.884V.

Although FADCs are fast (typical digitization 10ns or a bit better now a days set by settling time of comparato r and encoding time), they have poor differential linearity (because of the resistors) compared to other methods and the cost of comparitors (you need 2<sup>n</sup> comparators, including the over-range comparitor) limits the resolution. Next time, we'll look at clever ways of getting high precision ADCs. FADCs are commonly used for waveform measurements. Good (i.e. the fastest and most expensive) digital scopes use FADCs.